手搓cpu成功!

辛九八七六:

辛九八七六:

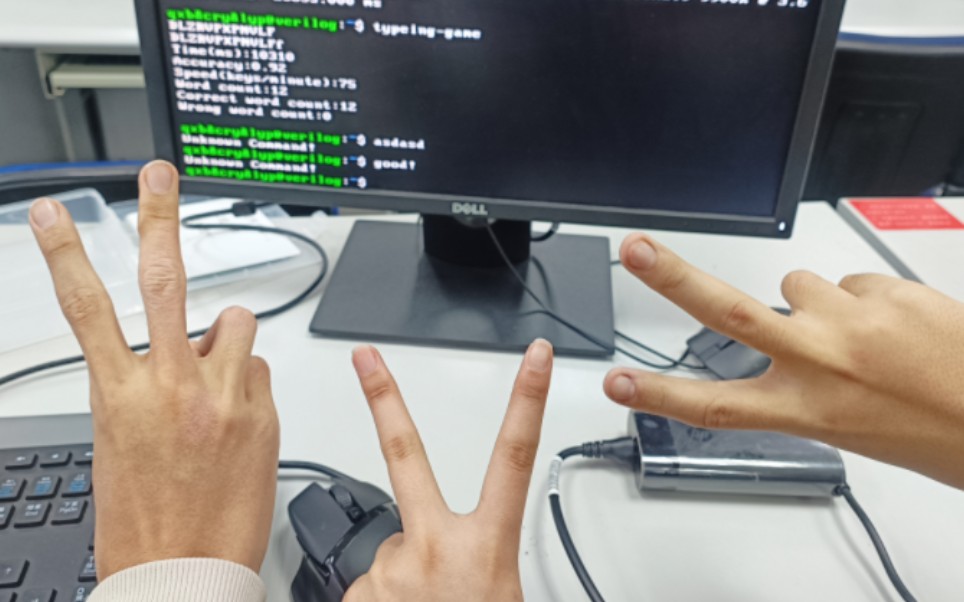

评论区的各位质疑的先别急。CPU我们是用verilog从ALU,指令解码器,立即数生成,跳转控制,分频器,RAM,ROM,寄存器(实地址寻址没有实现cache),冒险处理一步步搭建起来riscv框架cpu,包括键盘输入通码和断码的判断存储处理和VGA的显示缓存及接口这些一步步搭建起来的,是FPGA设计,用的学校发的Digilent Nexys A7-100T 开发板。这个视频只是记录一下我们在自己完成的cpu上运行的指令执行效果,不是在录制教学视频,我愿意拍大家都可以看得懂的软件,如果贴上硬件实现的代码会有一定的理解门槛。

【回复】看不懂硬件和CPU架构就不会点开这个视频,点开的都是看看你是怎么实现的硬件结构,结果只有一堆shell语言,所以大部分人都很失望[doge]

【回复】还有手搓,看了评论和简介,好像没有硬核到手搓那个程度吧,还是不要用这个标题[doge]

【回复】回复 @辛九八七六 :[doge]评论区想要看的是硬件,没事哥们,做的挺牛逼的,我们大二上学计组也写过verilog CPU,感觉现在这种课设都是标配了@辛九八七六 0x7c25c:

0x7c25c:

给不懂的人介绍一下,演示的是南京大学数字逻辑与计算机组成(DLCO)实验课大作业,基于RV32I指令集用verilog实现单周期或五段流水线CPU,然后整合前述实验中实现的键盘,VGA外设,并利用C/C++和RISC-V编译工具链实现软件部分,将.v文件生成二进制流烤到FPGA开发板上进行功能演示。

顺便吐槽一下这门课全靠自己动手完成,老师就前两周讲了一下verilog基本语法介绍了一下vivado,然后就是每周发布任务,上课时间全在验收实验和答疑,完全不讲课。

up这个大作业应该是做了选做部分,必做部分只有命令行基础命令(虽然我还没有开始做,期末赶各种ddl真的痛苦[笑哭])

【回复】一看这个描述就回忆起本科的噩梦。只讲了verilog基础语法要求实现这样一个庞大的体系,最难的事情感觉是根本不知道从何开始[笑哭][笑哭]别说答疑了,问题都不会问。当时本科大一学了编程语言马上就要做课程设计,也是只讲了基础语法,真绷不住了。

【回复】双非表示,长见识了,看见差距了,呜呜呜[大哭][大哭][大哭][灵魂出窍][灵魂出窍]俺们全部是浪费生命的水水课

【回复】看到评论区问 cpu呢 的真的气笑了,为什么能什么都不懂还理直气壮啊[笑哭] 同神明-观人间:

同神明-观人间:

不是,这玩意首先是基于fpga开发板上边模拟的,而且展示的是在cpu上边跑的软件功能(验收也是验收的这一部分,因为没cpu你压根就没法跑),并不是直接自己焊电路板搞的cpu,所以看起来视觉冲击力没那么强?

还有就是,这玩意看起来总比那代码好看吧,如果你水平真的很高想看到点有价值的东西,想看硬件设计代码大可去github和csdn上去看大佬写的,也没必要在这地方看吧,up只是想记录一下自己奋斗许久的结果,起了一个本来就是大实验最基础的要求的名字(敲代码写cpu不算手搓?...),结果评论区某些人就在这上纲上线,说实话真的很没必要

【回复】说的太好了哥![脱单doge] (我真没想到现在的互联网戾气这么重...

【回复】没办法,点进来的一部分人,是希望别人讲代码讲架构手把手交怎么做

宁一部分人,是看看有没有“高新技术”,“拽上天”的名场面

游戏选错了,换个雷霆战机效果会好点,或者自制贴几个原神启动的图

我进来纯粹是我想进来[doge]

【回复】什么时候github和csdn并列了? 涵涵是只小土豆:

涵涵是只小土豆:

你们这评论区看得我血压高[吃瓜]这不是南大的digital design的大实验嘛,好像还是在机房拍的。做到这种程度已经是非常好了,这么多不懂的人不知道在评论啥子[辣眼睛]

【回复】你看评论区能血压高为什么看标题不会血压高? 都可以talk:

都可以talk:

讲真的,我搞不懂为什么会有这么多人认为这不算“手搓”,从本质上讲用Verilog一类的硬件描述语言写一个能运行操作系统或者二进制程序的CPU已经算是自己独立完成了一个CPU设计的程度了吧,至于纠结什么“流片”,“焊芯片”一类的,应该没理解什么叫硬件描述语言吧🤔,还有什么软硬件都是自己的才叫手搓,我寻思着up只说了手搓CPU,也没扯操作系统啊,说真的国内有些计算机专业缺了点计算机系统和体系结构的知识了

【回复】你在说之前看看标题:手搓cpu成功

cpu和用verilog写系统设计是一个东西吗[辣眼睛]技术难度不是一个档次的,这么说算不算是引流标题

【回复】这肯定不算手搓啊,Verilog属于比较简单的了,很多计算机专业都有Verilog跑仿真CPU的课。

【回复】回复 @辛九八七六 :主要是大家认为的手搓cpu是像那些大佬一样焊线做8位cpu那种 ZeuRy骤离:

ZeuRy骤离:

你倒是多拍两下硬件啊,这软件效果写个C完事了,手搓CPU应该是组装ALU CACHE RAM等等吧,然后把汇编指令改成二进制机器码丢进去跑,看了半天光看你玩软件了

【回复】CPU我们确实是用verilog从ALU,指令解码器,立即数生成,跳转控制,分频器,RAM,ROM,寄存器(实地址寻址没有实现cache),冒险处理一步步搭建起来riscv框架cpu,包括键盘输入通码和断码的判断存储处理和VGA的显示缓存及接口这些一步步搭建起来的,是FPGA设计,用的学校发的Digilent Nexys A7-100T 开发板。但是我这个只是记录一下我们在自己完成的cpu上运行的指令执行效果,不是在录制教学视频,我愿意拍大家都可以看得懂的软件,如果贴上硬件实现的代码会有一定的理解门槛。如果你要看Makefile生成二进制代码再让vivado生成bitstream的五六分钟过程我倒是也可以给您单独录一期。

【回复】什么叫写个C就完事了,你到底懂不懂啊,就知道个啊。

【回复】我真服了,我评论没说up技术不行吧?单纯说个视频没有具体内容一堆人上来尬喷😅,我虽然是做软件的好歹也是自己写过五级流水线mips指令集cpu的😅,技术含量不高也不至于谁都要来喷两句吧😅 呵呵战士哎:

呵呵战士哎:

我以前在南大上数电的时候真是水的一笔,现在这课程大作业真不错啊 ,想要更进阶一点可以参加一生一芯

【回复】这个是数电实验,现在和数电课分开(课程改革了袁老师太厉害了) -y方:

-y方:

这个当时做吐了,一个bug找了一周,最后不知道怎么就调过了。不过当时操作系统什么都没上,还要写进去很难受。

【回复】对的,主要是大二的知识水平真不高,操作系统都没学,也没有小班pa的教学优势[委屈]

【回复】回复 @辛九八七六 :但是去年可以在家写一整个寒假(指pa和数电实验),就非常爽

【回复】回复 @辛九八七六 :南大不是人人都做PA的吗? LexBanner:

LexBanner:

看了评论区,只觉得国内本科教育任重道远[辣眼睛]

【回复】稍微了解一点的看评论区真的辣眼睛,血压高。

【回复】呃呃,这就是个素质问题 小白ono:

小白ono:

大家都理解成了搓硬件是大家的问题?

【回复】回复 @小白ono :这标题确实哗众取宠 第一眼让人误解 不过我确实在b站看过手搓cpu的视频[嗑瓜子]

【回复】回复 @小白ono :所以说你不懂啊,这就是纯正的,可以用,可以跑程序的CPU。反而b站上大多数所谓手搓CPU的视频都很“标题党”,因为压根用不了。为什么没有实体物件,因为即使是这种程度的真CPU造出来也是要不少钱的,所以都在FPGA板子上模拟。

【回复】回复 @wheresmyfuture :“确实手鲁过cpu” 太牛了 海绵宝哥和派派曦:

海绵宝哥和派派曦:

这个课设不错呀,这么过一遍基本verilog数电微机原理操作系统编译原理数据结构啥的就都了解差不多了,如果时间给的也充足的话好好做一下还是很有提高的,能普及一下就好了

【回复】说得好,但是这个cpu的大实验我自己单干的[大哭] DavidXie03:

DavidXie03:

真的离谱,看来国内把cpu设计纳入课程体系的学校还是太少了(或者懂哥太多),up这个是用Verilog设计的cpu,怎么不能算手搓了,难道得用电烙铁一点点把元件粘上去才算手搓吗[辣眼睛] Dr坚果:

Dr坚果:

隔行如隔山,网分,频谱仪上的曲线能按照我设计的出来我都能乐呵半天,但是不懂得只会觉得就这,一大堆乱七八糟的曲线有啥乐的[笑哭] 忆阁君QWQ:

忆阁君QWQ:

天哪,这比我学校学的数电课的难度大多了,我们最后只是用了verilog编了一个基于mips的单周期流水线,最难也就是单周期流水线的扩展😭😭羡慕南大

【回复】如果有点兴趣可以跟着置顶讲义做一下[脱单doge]