LDO基本原理与仿真实现(一)

好运的团子同学:

好运的团子同学:

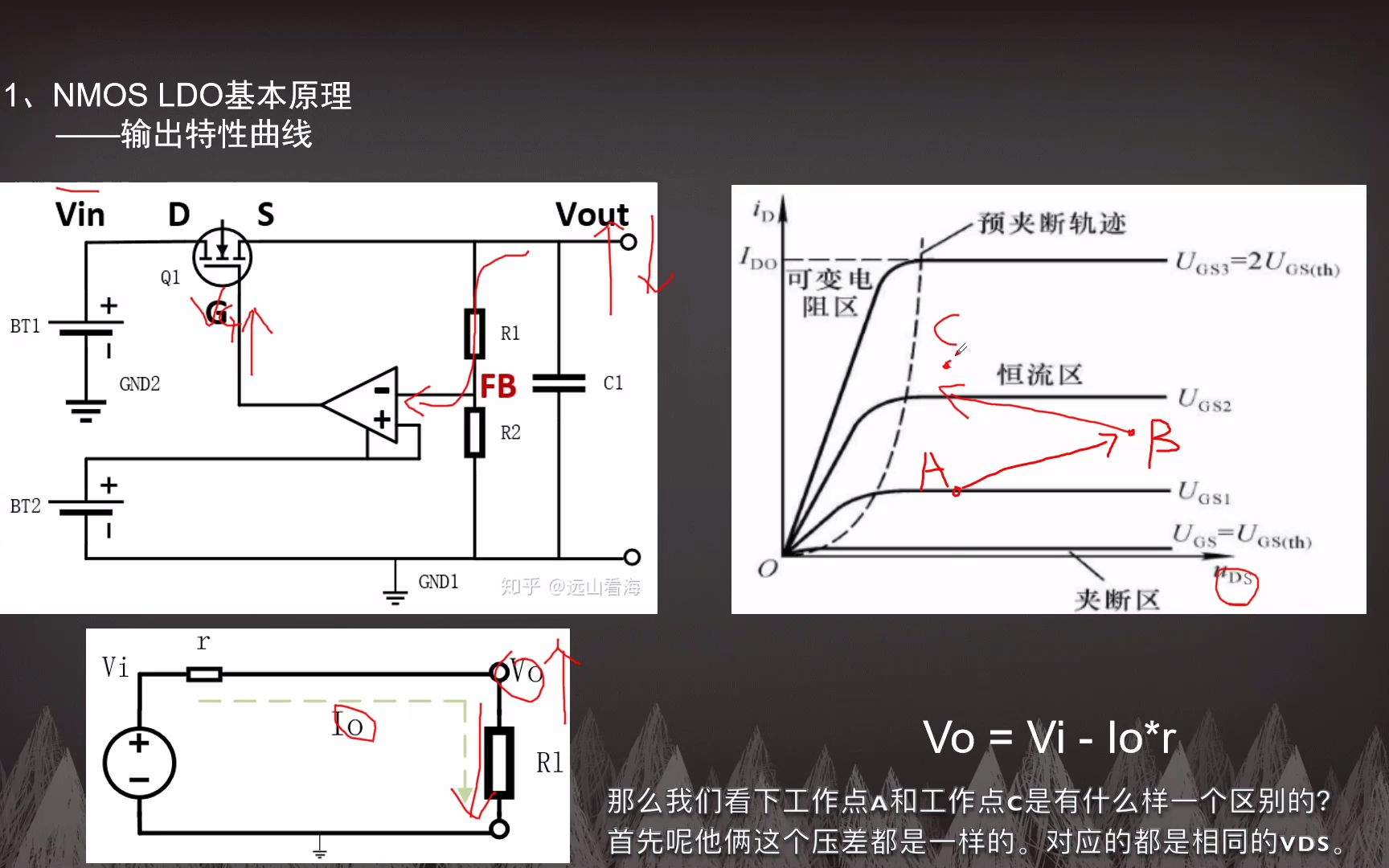

LDO是“低压差线性稳压器件”,那么该电路的目的落脚在保证Vo稳定不变。定性理解up给的 Vo=Vi-Io*r 这个式子,为了保证Vo稳定,在Io增大时需要降低r。将左上角位于恒流区的NMOS理解为可变电阻器(阻值随VGS增大而减小),放大器amp的存在使得Io增大时VGS增大,进而实现r的降低。 工程师看海:

工程师看海:

07:46,7分46秒的地方,讲的快了一步先把结论给抛了出来,补充下,刚开始Vo是降低的,状态由A到B,随着Vg(Vgs)上升,导致Vds压差减小,Vo又渐渐上升回来,这就是说的Vo上升、Io上升的由来,非常绕

【回复】Vgs上升,为什么Vds压降减小

【回复】回复 @工程师看海 :我觉得应该是vgs对电流变化的控制能力是大大强于vds的控制,当vg变大,加上之前vo减小,这里会对电流有一个超额补偿,所以vo不需要那么大,变小一点就行

【回复】回复 @工程师看海 :我感觉您视频下面这个电压源电阻分压模型不太对,或者说,需要调整。我们假设一下,如果整体电流增大,而电压源内阻、负载电阻都不变的话,会导致这两个电阻所分到的电压都增大,其结果就是只能电源电压增大——只有这样才能满足该假设情况。但估计up主想讲的并不是这样的应用场景。

更实际一点,我们是不是可以将场景调整为,负载电阻减小,导致整体电流增大,输出电压减小这个模型呢? 并不存在此用户:

并不存在此用户:

我个人有一些理解,不知道对不对。我觉得这里应该把输出电容考虑进去,这个很重要。负载电流增加的瞬间,其实MOS管电流是不变的,是输出电容放电补电流。电容放电导致Vout降低,Vout降低导致误差放大器输出增加,Vgs增加,Vgs增加导致mos电流增大,mos电流增大后给电容充电。电容充电后Vout升高重新进入稳态。不知道我讲的有没有问题~

【回复】按up讲的逻辑,输出电流增大的瞬间,反馈还没进行,vgs还没变化,那么ID是不会变动的。所以我认为此时增加的电流是输出电容提供的。当然这也是我个人的想法,希望可以和大家讨论学习 电器小医生:

电器小医生:

已投币,请问nmos的ldo和pmos的有什么区别

【回复】nmos一般电流大,需要额外有偏压

【回复】请问Io增加的话,那负载R是不是就降低了,

【回复】回复 @52wxx :理清你的需求,一般不建议自己做 工程师看海:

工程师看海:

喜欢的同学记得一键三连,关注公众号:工程师看海[来古-沉思]

【回复】你最后这里说的都错的,你自己好好看看吧

【回复】回复 @高端玩家2021 :07:46,7分46秒的地方,讲的快了一步先把结论给抛了出来,补充下,刚开始Vo是降低的,状态由A到B,随着Vg(Vgs)上升,导致Vds压差减小,Vo又渐渐上升回来,这就是说的Vo上升、Io上升的由来,非常绕。视频突然抛结论,是会让人蒙圈。。。。 古my:

古my:

最后应该是VGS增大,导通电阻r减小,使Vo增大;Io和r一定是相反着变化才会使Vo稳定。 吃不胖的巧克力猪:

吃不胖的巧克力猪:

看了这个视频觉得讲的很清晰,但是当输入电压突然变大的时候,负载不变,又是怎么样的调节过程。

【回复】输入电压升高是MOS的Vds升高,Id变大,输出电压升高,误差放大器检测到反馈电压升高从而降低MOS的Vgs以降低Id,逐渐稳定使得R2分压仍然等于Vref 未来一定会来:

未来一定会来:

其实可不可以理解为 vout=io*Rl然后负载电阻变了,要保持这个电压不变,就只能改变io vout减小就要增大io vout变大就要减少io通过pmos管来控制 平衡点是vout等于某个值 青城墨白雪:

青城墨白雪:

轻载就是在可变电阻区好吧,自己说的太绝对了 胡一八hpy:

胡一八hpy:

支持,微信公众号里关注的,希望以后多出视频 咖啡饼干呗:

咖啡饼干呗:

up您好,电源管理芯片,大部分datasheet中会有静态电流Iq的参数,部分datasheet会有转换效率Efficiency,搞不懂这两个什么区别,我在设计低功耗电路时候,在电源芯片选型时,应该选择哪种呢?[小电视_困惑]

【回复】回复 @小米气态键盘 :好的!多谢UP主指点![支持]

【回复】LDO基本不会提转换效率,通常提转换效率的是开关式DCDC,例如MP1584EN这种。Iq就是输出电流为0时IC的耗电,和运放的静态电流基本上是一个东西,LDO内部的核心元件也是一个运放加一个基准,在设计低功耗设备的时候更多的应该考虑静态电流。LDO和开关式DCDC的选择是看纹波需求,压差和电流需求 ilincs:

ilincs:

up你好,这个op和mos有推荐型号吗,谢谢