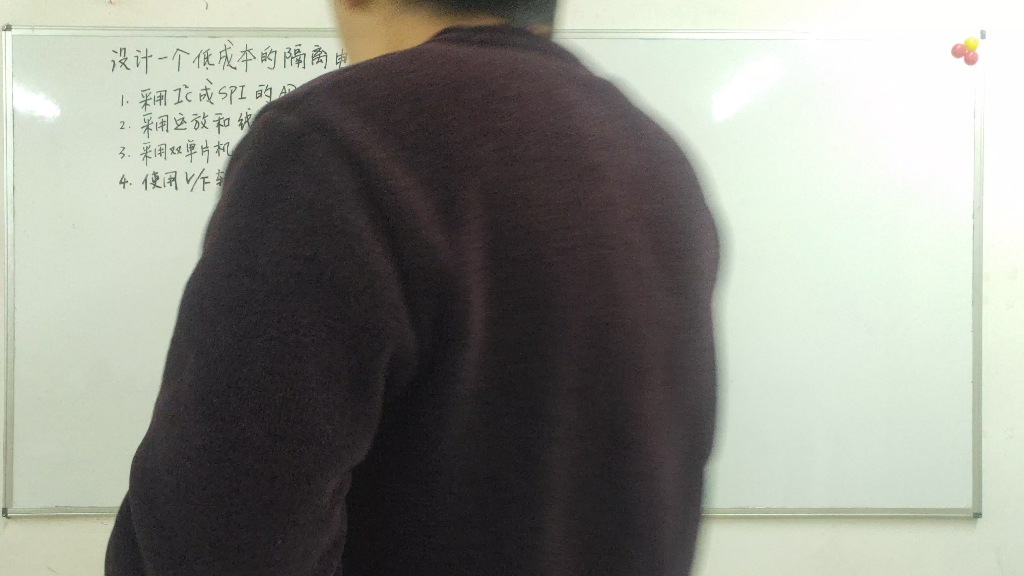

【电路设计】设计一个低成本的隔离电压采样电路

大涛哥哥_t:

大涛哥哥_t:

中心思想是让输出脉宽随外部输入信号变化,但这个精度不高吧,1、运放在被采样的原边,还需要一路隔离的电源为运放供电,增加了设计难度2、如果需要采多个隔离电压,每一路电压都需要单片机去读取脉冲信号,很占用单片机的资源,此电路将不再适用;3、VERF的作用不叫校准,而是提供一个基准使这个电路系统能够震荡,在无外部输入电压时,此电路也输出一定宽度的脉冲,输入电压和脉宽应该不是线性关系,个人觉得这个电路不太可靠。我提供一个电路作为参考,使用PC817光耦采样模拟电压,让光耦的LED电流随外部电压变化,光耦的输出侧根据CTR值配置在线性区,即可实现隔离采样。电路缺点是,光耦会受温度影响 my越过山丘:

my越过山丘:

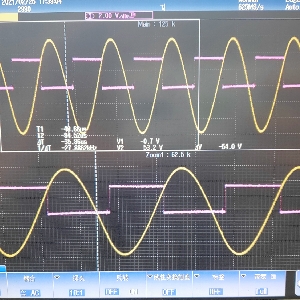

谢谢老师,用三极管确实会影响输出波形

【回复】你是个认真的人…有问题可以问我。我知道的都会和你说。 电器小医生:

电器小医生:

感谢老师,multisim上模拟了一下,结果很准,双币奉上

【回复】朋友,你在multisim上模拟的工程可以发我一下吗 回忆最美2734:

回忆最美2734:

老师,我请教你一下,这个电路如果VI小于VREF这个公式还成立吗?

【回复】很高兴你确实真真切切理解了,所以我也很真切地回答。你说得没错,这种情况自然是不成立的。所以比较适合对比较高的电压进行检测。 minkeyyyyy:

minkeyyyyy:

没明白自校准的意思是啥,另外除了考虑设计目的,mos管导通时间工作稳定性没有说明呀

【回复】MOS导通电阻远远小于R2,可忽略。自校准的意思就是,如果信号不携带基准电压的相关信息,你怎么知道在等于基准电压的输入时对应的物理量(比如v/f转换方式下的频率输出)是多少呢? 风间___:

风间___:

请问这个电路在产品上已经有成熟的应用了吗? 风间___:

风间___:

直接通过大电阻进行隔离或者用隔离运放进行隔离不更加方便便宜吗?

【回复】回复 @AGAN的电路设计 :忽略上一条信息,那个错了,接OPA2690ID的是放大电流信号的,我们用的FPGA,FPGA和强电不共地了,我们的DCLINK电压VBUS+和VBUS-相当于做了一个差分分压再到TLC082:VBUS=540V,VBUS+通过2241Kohm电阻和8.25Kohm电阻分压到TLC082的+输入端,8.25Kohm接到FPGA的地,VBUS-接2241Kohm电阻到到TLC082的-输入端,然后-输入端接反馈电阻到输出,这就相当于把高压缩小了为原来的8.25/2241=0.00368,不管怎么样,这个确实比你那个方案贵了

【回复】回复 @AGAN的电路设计 :我们用的FPGA,而且FPGA和低频整流的地或者说是DCLINK电容的地连在一起的……不过我们用的运放是OPA2690ID做等比例放大,比你那个LM358贵多了[呲牙]我错了,没想到我们这个运放这么贵,我也是看了你的视频查了下这颗运放的价格……

【回复】回复 @Furious1986 :没事没事,大家互相学习 今古恨几千般123:

今古恨几千般123:

老师,采样原边电压到副边可以使用这个电路吗? iqfsto:

iqfsto:

老师,请问积分电路里面的那个电容可以随便取值吗? 名叫兔兔的猫:

名叫兔兔的猫:

老师,第二个运放是怎么实现限制输出是在1/3到2/3Vcc之间的方波呢?[脸红]

【回复】三个电阻分压,其中一个接运放输出。所以运放输出高就2/3,运放输出低就1/3